Display configuration

Table of content

1. Introduction

This section describes the display configuration registers.

These registers allow to configure the width, height and size of the

screen as well as the refresh address generation.

2. Registers

2.1 DISPLAY_WIDTH

| Address: 0x10 |

Display pixel width |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| D_WIDTH[15:8] |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| D_WIDTH[7:0] |

| | D_WIDTH | : Display pixel width |

2.2 DISPLAY_HEIGHT

| Address: 0x12 |

Display pixel height |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| D_HEIGHT[15:8] |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| D_HEIGHT[7:0] |

| | D_HEIGHT | : Display pixel height |

2.3 DISPLAY_SIZE_LO / HI

| Address: 0x14 |

Display pixel size low (bits 0 to 15) - DISPLAY_SIZE_LO |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| D_SIZE[15:8] |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| D_SIZE[7:0] |

| Address: 0x16 |

Display pixel size high (bits 16 to 31) - DISPLAY_SIZE_HI |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| D_SIZE[23:16] |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| D_SIZE[31:24] |

| | D_SIZE | : Display pixel size (must be equal to D_WIDTH*D_HEIGHT |

2.4 DISPLAY_CFG

| Address: 0x18 |

Display configuration register |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| res. |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| res. |

D_X_SWAP |

D_Y_SWAP |

D_CL_SWAP |

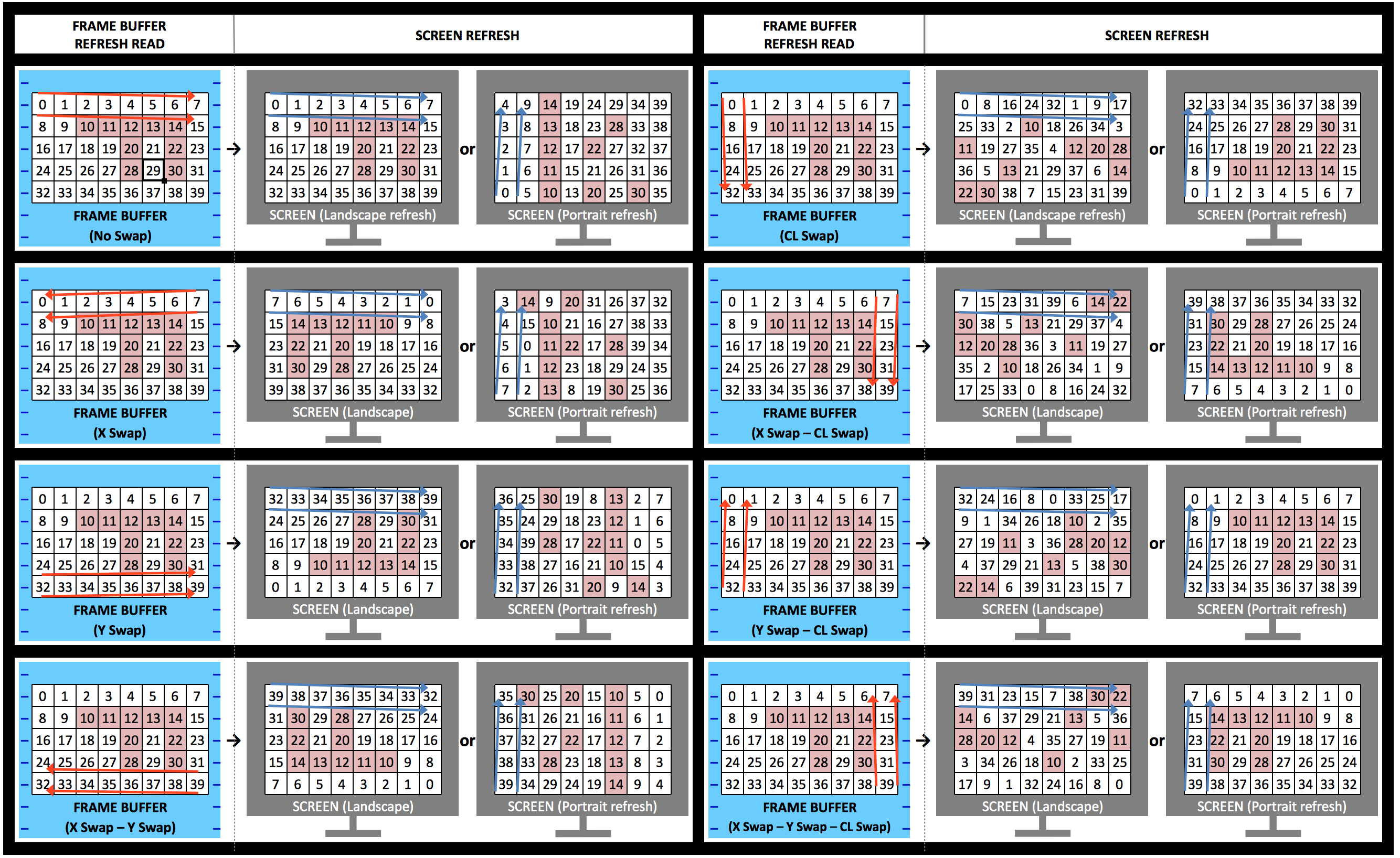

The D_*_SWAP configuration registers allow to control in which order the frame buffer pixels are read during a screen refresh.

| | D_X_SWAP | : X-axis address generation for the frame buffer read during screen refresh

0 = scan rows from left to right

1 = scan rows from right to left |

| | D_Y_SWAP | : Y-axis address generation for the frame buffer read during screen refresh

0 = scan columns from top to bottom

1 = scan columns from bottom to top |

| | D_CL_SWAP | : Swap Columns and lines for the address generation of the frame buffer read during screen refresh

0 = horizontal scan (i.e. read along the rows)

1 = vertical scan (i.e. read along the columns) |

The following table illustrate how the frame buffer is read according to the different configurations, and how the

picture will look like on the screen, depending on how the screen is refreshed.

2.5 DISPLAY_REFR_CNT

| Address: 0x1A |

Display refresh counter |

| 15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

| D_REFR_CNT[15:8] |

| 7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

| D_REFR_CNT[7:0] |

| | D_REFR_CNT | : The display refresh counter can be initialized to any value by software

and will be automaticaly decremented after each screen refresh until it

reaches 0x0000.

The IF_RCDONE interrupt flag is set when the counter reaches 0x0000. |